용 후아 지아 / 코덱개발팀, 유아 푸 자오 / 임베디드 개발 엔지니어

히크비전 / www.hikvision.com

빠르게 확장되고 있는 비디오 감시 영역에서, 수요자들은 더 낮은 가격 및 전력을 이용하여 보다 높은 해상도, 보다 많은 채널, 그리고 연산적으로 용이한 해석이 가능하기를 요구하고 있다. 이 글에서 우리는 디지털 비디오 리코더(DVR), 디지털 비디오 서버(DVS) 및 감시 IP 모듈의 선도업체인 히크비전이 최신 제품에 이러한 요구들을 어떻게 만족시켜 왔는지에 대해 연구한다.

히크비전(HikVision)은 TI의 다빈치 프로세서를 이용하여 디지털 비디오 리코더(DVR), 디지털 비디오 서버(DVS) 및 독립형 비디오 IP 모듈을 포함하는 비디오 감시 제품이 어떻게 만들어지게 되었는지를 설명한다.

빠르게 확장되고 있는 비디오 감시 영역에서, 수요자들은 더 낮은 가격 및 전력을 이용하여 보다 높은 해상도, 보다 많은 채널, 그리고 연산적으로 용이한 해석이 가능하기를 요구하고 있다. 이 글에서 우리는 디지털 비디오 리코더(DVR), 디지털 비디오 서버(DVS) 및 감시 IP 모듈의 선도업체인 히크비전이 최신 제품에 이러한 요구들을 어떻게 만족시켜 왔는지에 대해 연구한다.

하드웨어 선택

기존 제품에서, 히크비전은 ARM 프로세서와 짝을 이루는 TI의 TMS320C6000 DSP를 사용했다. 이 조합은 제품을 서로 잘 보완하지만, 보다 많은 채널 및 더욱 향상된 화질을 추구하는 수요자의 요구를 만족시키기 위해서는 더 많은 성능이 필요했다.

차세대 플랫폼을 선택함에 있어 성능, 소비 전력, 가격 및 개발 용이성과 같은 많은 요소들이 평가되었다. ASIC 기반 솔루션은 최저 소비 전력 및 단가 당 고성능을 제공하였다. 그러나 ASIC은 몇 가지 문제점을 드러낸다.

그 중 하나는 시간 및 경제적인 면에서 점점 증가하고 있는 높은 개발 비용이다. 디자인 비용을 충당하기 위해서는 엄청나게 큰 액수가 필요하다. ASIC의 또 다른 문제점은 융통성의 부재이다. ASIC은 긴 디자인 주기를 갖고 있기 때문에, 변화하는 수요자의 요구에 효과적으로 대응할 수가 없는 것이다.

FPGA 및 MPP(massively-parallel processors)는 프로그래머빌러티(programmability) 및 부가적인 비디오 채널을 제공하면서도, 프로그램하기가 어렵다는 점에서 이들 디바이스도 고유의 결점을 갖는다. 저렴한 가격으로 낮은 전력을 소비하고, 간단한 프로그래밍 모델을 유지하며 더 많은 성능을 제공하는 쉽고 프로그램 가능한 솔루션이 요구된다.

TI 프로세서를 선택하는 데에는 몇 가지 이유가 있다. 가장 큰 이유는 코드 재활용이다. 히크비전은 TMS320C64x DSP에 고도로 최적화된 코덱을 수행하는 중요한 리소스에 투자했다. TI의 차세대 DSP는 C64x 디바이스와 코드 호환이 가능하기 때문에, 기존 코드의 포팅(porting)은 최소의 노력으로 가능하다.

또 다른 이유는 툴이다. 히크비전의 엔지니어들은 검증된 개발 환경 및 방대한 단위의 설비를 제공하는 TI의 코드 컴포저 스튜디오(Code Composer Studio)에 익숙하다. 또 가장 중요한 점은 TI의 로드맵은 다빈치 계열의 디지털 미디어 프로세서를 진행시킬 수 있는 보장된 방법을 제공했다.

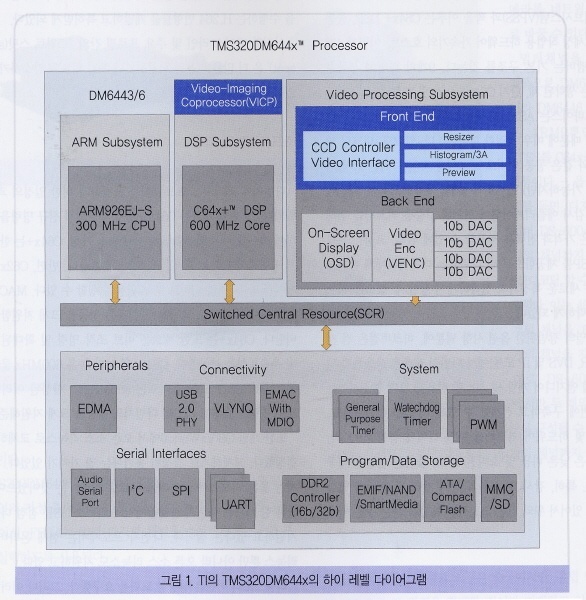

그림 1. TI의 TMS320DM644x의 하이 레벨 다이어그램

TI의 다빈치 포트폴리오는 TI의 최고 성능 TMS320C64x+ DSP 코어에 기반 한 14개의 디지털 미디어 프로세서를 포함한다.

그 계열의 플래그십 디바이스(그림 1 참조), ARM9 및 비디오 프로세싱 서브시스템(VPSS)과 짝을 이루는 C64x+ DSP, 공통 비디오 프로세싱 작업용 하드웨어 가속기의 호스트, 이렇게 4개의 다빈치 멤버는 기본 구조를 갖는다. 9개의 다빈치 부품은 ARM 코어는 생략된 채, 단지 C64x+ core 및 VPSS만 갖는다.

다빈치 디바이스는 ASIC 및 프로그래머블 DSP간의 균형을 잘 맞춰주기 때문에 매우 적절한 디바이스다. 인코딩, 디코딩 및 디스플레이와 같은 공통 비디오 프로세싱 작업을 위한 고정 기능(재구성이 가능하지만) VPSS 가속기를 제공함으로써, 다빈치 디바이스는 감시 애플리케이션에 연관된 고중량 리프팅을 위해 ASIC과 같은 가격과 전력을 제공할 수 있게 된다. 고성능 프로그래머블 DSP를 제공함으로써, 다빈치는 디자이너에게 콘텐츠 해석과 같은 새로운 특징까지 신속하게 수행할 수 있도록 하는 유연성을 허락하게 되었다.

다빈치 계열의 광범위한 옵션 사항 덕분에, 히크비전은 전 제품 라인(DVR, DVS 및 IP 모듈)에서 다빈치 제품을 사용하게 되었다. 때문에 엔지니어 개발 및 시스템 비용을 크게 감소시키는 방안을 한 번에 구축하고 전개할 수 있게 하였다. 추가적으로, ARM 코어 및 하드웨어 가속기를 단일 다이에 통합함으로써, 다빈치 부품은 낮은 비용 및 소비전력으로 증가된 성능을 제공하게 되었다. 특히, 감시 IP 모듈과 같이 가격 및 전력에 민감한 제품들에 있어서 위와 같은 고도화된 통합을 하는 것은 매우 중요하다.

소프트웨어

비디오 감시 영역은 경쟁이 치열하다. 낮은 전력 및 가격의 ASIC솔루션과 경쟁하기 위해서, 히크비전은 소프트웨어에서 장점을 찾았다. 소프트웨어의 유연성을 활용하여, ASIC의 디자이너보다 수요자의 변화하는 요구에 더욱 효과적으로 응답할 수 있게 되었다.

히크비전의 연구개발 예산 중 상당 부분이 이미 비디오 코덱 개발쪽으로 넘어갔다. 비디오 감시에 적합한 고도로 최적화된 비디오 코덱을 개발함으로써, MIPS 의무를 낮게 유지하면서도 경쟁자들보다 좋은 화질을 제공할 수 있게 되었다.

가령, 인터레이스 및 B 슬라이스를 포함하는 주요 프로필의 특징을 선택할 수 있을 뿐만 아니라 H.264 베이스라인 프로필을 수행하는 H.264 변형물을 개발하고 특허받게 되었다. 이러한 베이스 라인 및 주요 프로필 간의 '스위트 스팟(sweet spot)'은 더 많은 비용을 요구하거나 채널 밀도를 감소시키는 일 없이 더 좋은 화질을 제공할 수 있게 되었다.

소프트웨어의 과제

다빈치에 레거시 소프트웨어를 포팅하기 위한 일정의 과제가 있었다. 첫 번째 과제는 C64x+ 명령 세트에서 신규 명령을 활용하여 코드를 다시 최적화하는 것이었다. 가령, C64x+는 한 사이클 당 8개의 16비트 MAC 명령까지 수행한다.

반면, C62x는 한 사이클 당 두 개의 16비트 MAC만을 수행할 수 있다. MAC 집약적인 오디오/비디오 코덱에서, 이것은 성능을 크게 지원함을 의미한다. C64x+는 또한 새로운 비트 조작 명령 및 확대된 부가 및 추출특성을 제공한다. C64x+의 보다 높은 600MHz 클록 레이트(최대 C62x 클록 레이트는 300MHz)와 합성된 이러한 새로운 명령은 솔루션 기반의 다빈치의 성능을 크게 지원해준다.

또한 개인 OS(VxWorks)에서 오픈 소스 리눅스로 교체하기로 결정했다. 교체하기로 결정한 동기에는 몇 가지가 있었다. 한 가지는 물론 리눅스가 로열티를 무료로 해준다는 것이었으며, 또 다른 한 가지는 다빈치 플랫폼에서의 리눅스 OS를 점점 더 많이 지원하고 있다는 점이다. 다빈치 프로세서는 현재 몬타비스타 리눅스 뿐만 아니라 오픈 소스 리눅스도 지원하고 있다.

리눅스로의 이전은 상당한 노력을 요구했다. 그러나 이러한 이전은 TI의 DSPLink의 리눅스 지원에 의하여 용이하게 되었다.

DSPLink는 ARM 코어와 DSP사이에 가상의 층을 제공하는 프로세서 간 통신 기술이다. DSPLink를 이용하면, ARM에서 운용중인 코드는 OS에 무관하게 DSP와 통신하고 있는 동일한 고레벨의 API를 사용하게 된다. 이러한 API는 다빈치 플랫폼에서 OS를 변경하는 것을 더욱 용이하게 해준다.

시스템 레벨 과제

보다 많은 비디오 채널을 처리할 수 있는 능력은 또 다른 과제를 가져다준다. 칩 내외부에서 보다 많은 비디오를 얻어야 한다는 것이다. TMS320DM6446 프로세서는 단일의 지정 입력 비디오 포트 및 단일의 지정 출력 비디오 포트를 갖는다. 칩의 부가적인 채널에 있어서, FPGA는 멀티 디지털 채널을 스트리밍하는 PCI 포트를 실행하도록 사용된다.

현재 솔루션

그림 2. 다빈치 및 오픈 소스 리눅스를 사용하는 히크비전 감시 모듈

그림 2에 나타난 감시 IP 모듈과 같은 단일 채널 입/출력 특성을 갖는 제품으로 TMS320DM648 DSP를 선택했다. 이 제품은 ARM 코어가 아니라 C64x+ 코어 및 VPSS를 포함한다. IP 모듈은 DM6446와 히크비전 특허의 H.264 알고리즘을 사용해 한 개의 비디오 채널을 압축한다.

이 비디오는 4CIF 해상도(4CIF = 4×CIF 해상도, 또는704×576 화소)에서 압축된다. 원(one) 채널 오디오 압축 또한 오그보비스(OggVorbis) 코덱을 사용하여 지원된다. 이러한 IP 모듈은 작고, 아주 작은 전력을 소모하며, 아날로그 카메라 내부에 매립되어 아날로그 카메라를 네트워크 카메라로 바꿀 수 있다.

멀티채널을 지원하는 제품으로 DM642뿐만 아니라 DM6446 - 이 제품은 ARM9뿐만 아니라 VPSS를 C64x+에 병합한 제품이다 - 을 선택했다. 예를 들면, 디지털 비디오 서버 DS-6004HCI는 네 개의 채널까지 동시 인코딩/디코딩 할 수 있도록 지원한다. 이는 4CIF에서 한 개의 채널을, CIF에서 세 개의 채널을 지원한다. 교대로, DS-6004는 단지4CIF에서만 두 개의 채널을 지원하도록 구성될 수 있다. 또한, 오디오 인코딩/디코딩의 네 개의 채널까지 오그보비스 코덱을 사용하여 지원될 것이다.

전망

현재, 히크비전의 주요 시장은 중국이지만, 유럽 및 북아메리카 시장으로 그 영역을 확대할 것이라 기대하고 있다. 예를 들어, 최근 우리는 프랑스 감시 솔루션 제공자들을 디자인 면에서 앞섰다. 히크비전은 이전부터 세 개의 다른 공급자들이 제공한 장치들을 이용하는 감시 솔루션을 만들고 있었다. 현재도 역시 DVR, DVS 및 독립형 IP 모듈에 부가하여 카메라도 판매하고 있기 때문에, 가장 낮은 가격으로 이들 세 공급자들을 대체할 수 있을 것이다.

시장 점유율 확대를 위해, 우리는 고객이 꿈꾸는 미래를 디자인하고 있다. 이는 단기간 내 더 낮은 프레임 비율이라면, 보다 높은 해상도 및 화질을 획득할 수 있음을 의미하며, 오랜 시간 내에는 고해상도와 고프레임 비율이 표준이 될 것임을 의미한다.

고객은 또한 비디오 해석을 요구하기 시작했다. H.264와 같은 진보된 압축 알고리즘은 더 많은 영상 데이터를 전송하고 저장할 수 있도록 한다. 이것은 채널 증가와 함께 비디오 시스템을 이끌게 되었다. 이러한 사실은 좋은 점도 있지만 문제점도 야기시킨다. 문제점은 어떻게 증가된 채널의 수를 모니터링할 것인지에 관한 것이다.

사람이 비디오를 모니터링하는 것은 비용도 많이 들고 오류의 가능성도 많기 때문에, 이상 활동(suspicious activity)과 같이 관심을 끌만한 상황의 비디오를 모니터링 할 수 있는 알고리즘이 필요하게 되었다. 그러한 상황에서 감시를 강화하도록 하기 위해, 알람을 울리거나 감시자에게 상황에 대한 정보를 보내줄 수 있다.

비디오 해석 또는 비디오 콘텐츠 분석(VCA)에 대해 많은 연구를 진행하고 있지만, 본 연구를 이용한 많은 양의 고객 제품에 대한 애플리케이션은 천천히 진행되고 있다. 주로 해석 알고리즘은 고도의 연산 조건들을 요구하기 때문이다.

그러나 다빈치와 같은 진보된 기술은 비디오 해석을 목표치까지 이르게 하고 있다. 인코딩/디코딩과 디스플레이에 연관된 고중량 리프팅을 수행하는 다빈치 하드웨어 가속기를 이용하면, 고성능 C64x+ DSP는 비디오 해석의 집중 프로세싱 조건을 다룰 수 있게 된다. 현재 히크비전은 첫 번째 비디오 해석의 특징인 안면 인식을 수행하기 위한 작업을 하고 있다.

그림 4. 다빈치 기술 및 오픈 소스 리눅스 사용 6100 시리즈 디지털 비디오 서버

미래의 요구를 만족시키기 위해서는 더 높은 성능을 필요로 하는 것이 당연하다. TI의 로드맵을 진행하면서, 현재 가장 최신 다빈치 프로세서인 TMS320DM6467(그림 4 참조)을 평가하고 있다. 이 디바이스는 비디오 감시에 있어서 몇 가지 유리한 점을 제공하고 있다.

하나는, DM6467디바이스가 강하게 결합된 인코더 및 디코더 코프로세서로 구성된 트랜스코딩 코프로세서를 통해서 중요한 성능을 지원할 수 있다는 것이다. 동시 인코딩/디코딩을 요구하는 DVS에서, 이러한 코프로세서는 연산적으로 용이한 해석이 가능하도록 C64x+를 배제함으로써 최대한 도움을 받게 된다.

감시 IP 모듈과 같이 단지 인코딩만 필요로 하는 제품에서는 디코딩 프로세서가 필수적으로 인코더 가속기의 서브셋이므로, 디코더는 인텔리전트한 방법으로 인코딩을 가속하는데 사용될 수 있었다.

DM6467 디바이스는 또한 PCI 포트를 추가한다. 이 포트를 사용함으로써, 우리는 멀티채널 DVS 및 DVR에서 FPGA의 요구를 생략할 수도 있다. 또한, DM6467은 단일 16비트 BT 입력과 출력으로 재구성될 수 있는 두 개의 8비트 BT .656 입력과 출력을 지원한다. 이는 DM6467이 두 개의 높은 해상도 입력을 갖는 감시 솔루션으로서 양호한 솔루션이 될 수 있도록 해준다.

저작권자 © CCTV뉴스 무단전재 및 재배포 금지